ترجمه مقاله مدلسازی مدار معادل IC رمزنگاری برای طراحی امنیت اطلاعات

ترجمه مقاله Equivalent Circuit Modeling of Cryptographic Integrated Circuit for Information Security Design

چکیده فارسی:

در مقاله حاضر، مدلسازی مدار معادل، برای ایجاد یک روش به منظور ارزیابی سیستم های رمزنگاری قبل از ساخت آن، بررسی شده است. مدل مدارمعادل یک FPGA رمزنگاری که در آن الگوریتم استاندارد پیشرفته ی رمزنگاری (AES) پیاده سازی شده، به وسیله اندازه گیری های تجربی، تحت پیکربندی اولیه ی یک شبکه ی توزیع توان FPGA – PDN مشخص شده است. مدل فوق، به طور یک شبیه ساز (simulator) تجاری مدار پیاده سازی شده است که در آن تریس های توان به منظور جریان نویز سوییچینگ همزمان، تحت سه پیکربندی مختلف PDN برآورد شده اند و یک مدار جداساز، به PDN به صورت on-board اضافه شده است. تریس های توان تخمینی، به منظور به دست آوردن مقادیر همبستگی، به طور آماری و با روش تجزیه و تحلیل توان همبستگی، به عنوان یک شاخص اصلی امنیت AES، بررسی شده اند. تغییر در مقادیر همبستگی و تغییرات در پیکربندی جداسازی، با نتایج تجربی مربوطه، سازگاری دارند. یعنی امنیت دستگاه های رمزنگاری در مقابل حملات side-channel (کانال-کناری) به کمک مدل مدارمعادل، پیش از ساخت، قابل ارزیابی می باشد.

دانلود مقاله اصلی در ادامه مطلب.

مقدمه:

در سال های گذشته، در تمام دنیا، شبکه های پهن باند (broadband networks) با توجه به تبادل حجم وسیعی از اطلاعات در سطح دنیا، رشد فزاینده ای را تجربه کرده اند. یعنی، نشت و دستکاری اطلاعات، به صورت مداوم در حال تبدیل به تهدیدهای واقعی به منظور امنیت اطلاعات، حتی در محصولات مصرف کننده، نظیر کارت های هوشمند، کامپیوترهای میزبان، کارت های حافظه، و دستگاه های سخنگوی خودکار می باشند. فناوری های رمزنگاری در ابتدا به منظور حفاظت از محصولات در برابر این تهدیدها، مورد استفاده قرار گرفته اند، با این حال ممکن است در آینده این روند ادامه نداشته باشد.

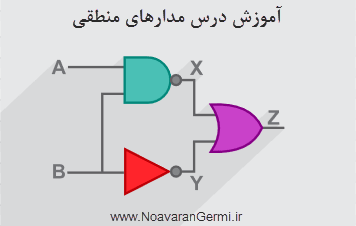

روش های حمله به دستگاه های رمزنگاری، که با نام حملات side-channel (کانال-کناری) شناخته شده هستند، با هدفِ ناکام گذاشتن تکنولوژی های رمزنگاری به وجود آمده اند. در 1999، کوچر و همکارانش، کلید رمز یک دستگاه رمزنگاری را با بررسی تریس های جریانِ توانِ فرکانس رادیویی (RF) در هنگام روشن بودن گیت های منطقی در مدارِ مجتمع (IC)، رمزگشایی نمودند. آن ها دریافتند که دامنه ی جریان نویز سوییچینگ (SSN) همزمان، به مقادیر یک رجیستر سوییچینگ، که موقتا مقادیر میانی را در یک فرآیند رمزنگاری ذخیره میکرد، مرتبط بود.

حملات side-channel (کانال-کناری)، حملات مرتبط با رمزنگاری ناشی از جریان SSN آی سی ها یا تابشهای الکترومغناطیسیِ حاصل از جریان SSN هستند. جریان SSN همانند گیت های منطقی در یک سوییچ آی سی رمزنگاری به طور همزمان در طول فرآیند رمزنگاری تولید می شود.

این جریان، شامل اطلاعات رمزنگاری محرمانه ای است که از طریق تجزیه و تحلیل آماری قابل استخراج است، زیرا تغییر جریان توان به فرآیند رمزنگاری بستگی دارد. یک مهاجم، جریان SSN و/یا تابش الکترومغناطیسی (EM) را مشاهده میکند، شکل موج های آن ها را به دست میآورد، و پس از آن برای شکستن رمز، مورد بررسی قرار می گیرند. بنابراین، وظیفه ی اصلی در طراحی یک سیستم رمزنگاری، برای تضمین امنیت در برابر حملات side-channel (کانال-کناری)، کاهش جریان SSN است.

در زمینه ی سازگاری الکترومغناطیسی (EMC)، روش های مختلفی برای کاهش جریان SSN و تابش الکترومغناطیسی (EM) به وجود آمده اند که اقدامات بالقوه ای برای مقابله با حملات side-channel (کانال-کناری) هستند.

چکیده انگلیسی:

In this study, equivalent circuit modeling was examined to develop a method to evaluate cryptographic systems before fabrication. An equivalent circuit model of a cryptographic FPGA in which an advanced encryption standard (AES) algorithm had been implemented was determined from experimental measurements under the initial configuration of a power distribution network (PDN) of the FPGA. The model was implemented into a commercial analog circuit simulator, and power traces due to the simultaneous switching noise current were estimated under three different PDN configurations in which a decoupling circuit was inserted into the PDN as an on-board countermeasure. Estimated power traces were analyzed statistically by the correlation power analysis method to obtain correlation values, a major security index of AES. Variation of the correlation values with changes in decoupling configuration agreed with the corresponding experimental results. This means that the security of cryptographic devices against side-channel attacks can be evaluated by using the equivalent circuit model before fabrication.

http://ieeexplore.ieee.org/xpl/articleDetails.jsp?arnumber=6487397

(26 امتیاز از 6 رای)

(26 امتیاز از 6 رای)

هیچ نظری ثبت نشده است